Benefits

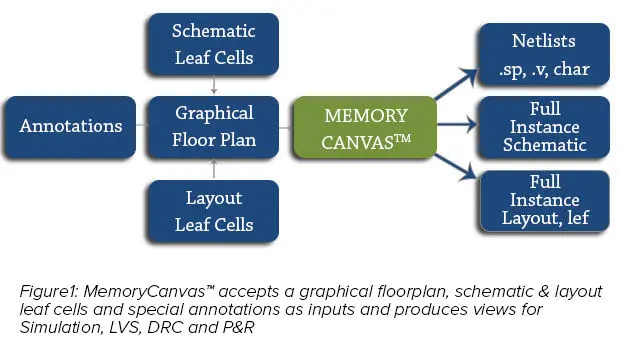

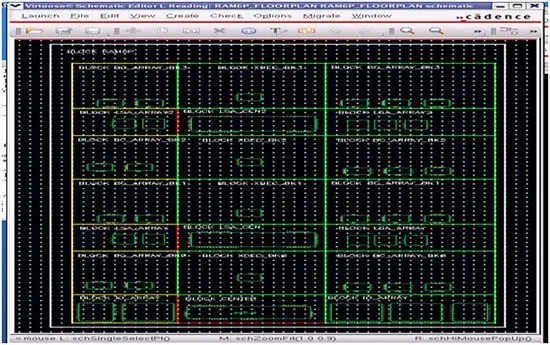

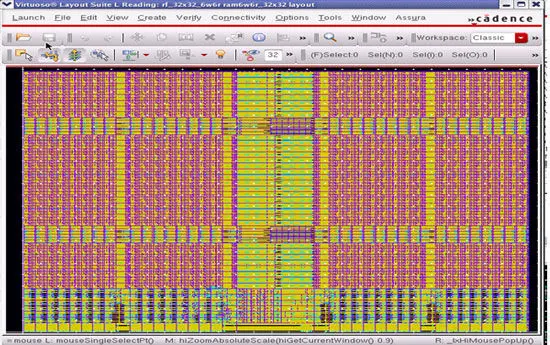

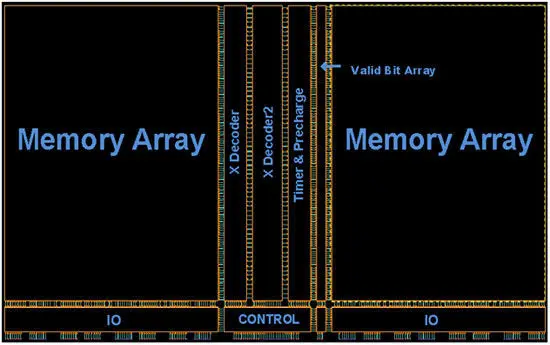

MemoryCanvas™ benefits the circuit design architect, layout designers, validation engineers, and compiler integrators. The floor plan provides an excellent means for designer and layout engineer to communicate assembly intent. The schematic and layout correspondence insures no mistakes in cell interfaces, signal directions and pitch matching constraints for all parameterization options. The easy-to-learn and exchangeable compiler format makes an ideal choice to standardize all corporate memory compiler development. LVS issues are minimized as correct-by-construction assembly between schematic and layout is assured while formal verification and netlist simulations insure functional compliance.

MemoryCanvas™ also supports the compiler characterization process. It automatically produces a configurable donut netlist (Fig 5), or a reduced Pi netlist. It integrates with existing netlist pruners/critical path methods. MemoryCanvas™ integrates seamlessly to existing commercial data collection and timing view engines.

MemoryCanvas™ is ideally suited to be used for producing instance families for complex memories such as Embedded Cache and Memories for whole standard parts. Through integration with standard EDA tools that support routing and chip assembly, users can quickly implement the memories and interfaces to the entire chip infrastructure for productivity improvement.