MemoryTime™

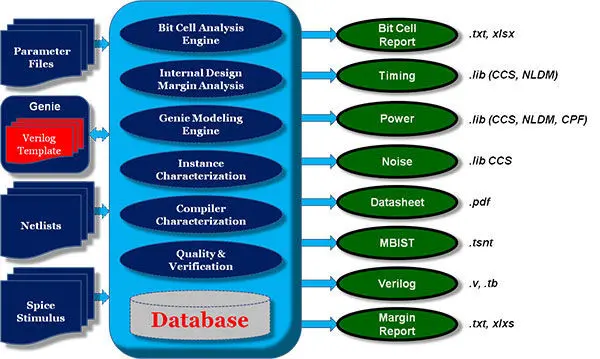

The rich set of features in MemoryTime™ enables the designers to quickly move thru the various phases of designing complex embedded memories.

Figure 2 - Data Flow

Product Description

MemoryTime™ benefits circuit designers, device engineers in foundries and memory compiler developers. The tool supports standard spice formats resulting in a fast learning curve. The various steps involved in memory design are effectively captured in a common database. This helps to insure design and data integrity. The job control facility allows designers to make the best use of compute resources. It also works with third party job control systems. MemoryTime™'s ability to accept multiple netlists and stimulus files enables simulations to be optimized for the particular task. For compilers, once a design is fully characterized a built-in estimator provides fast and accurate timing and power data. MemoryTime™ also supports a compiler distribution mode.

MemoryTime™ is also ideally suited for producing instance families for complex memories such as embedded Cache or CAMs. Through comprehensive automation of the memory modeling, characterization and data validation process, user's benefit in significant productivity improvement.