Key Features

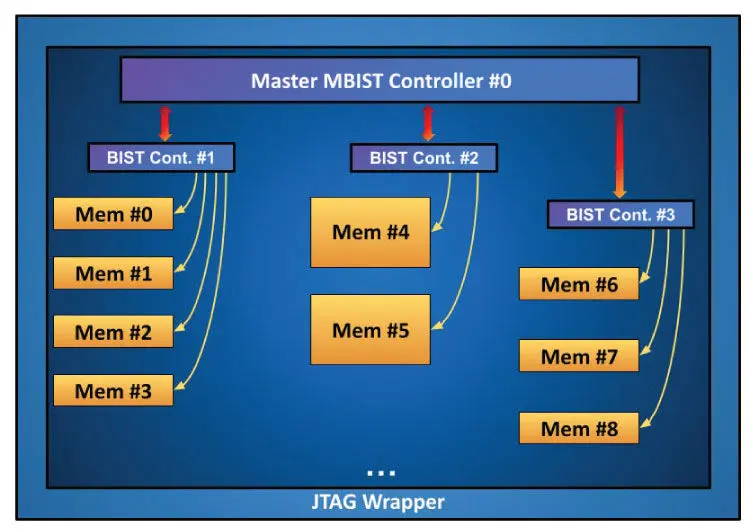

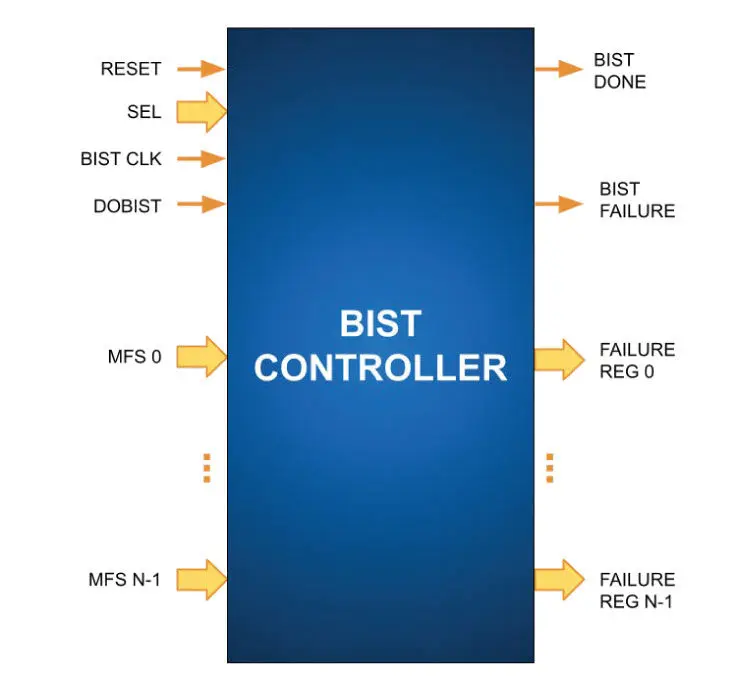

-> Multiple BIST Controllers

-> Built-In ECC

-> Multiport SRAMs, TCAMs, and RFs

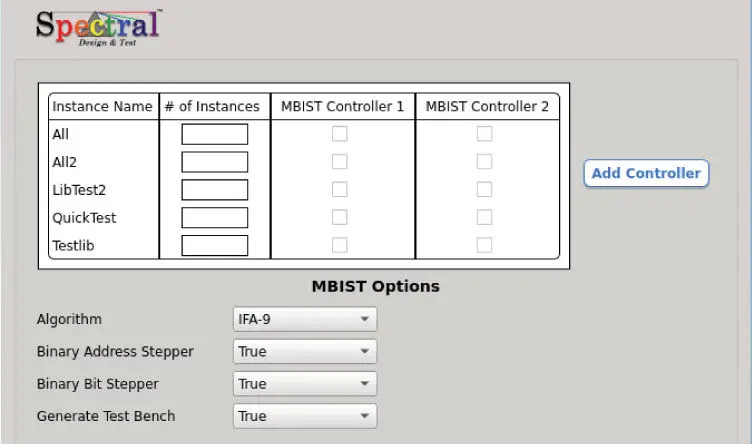

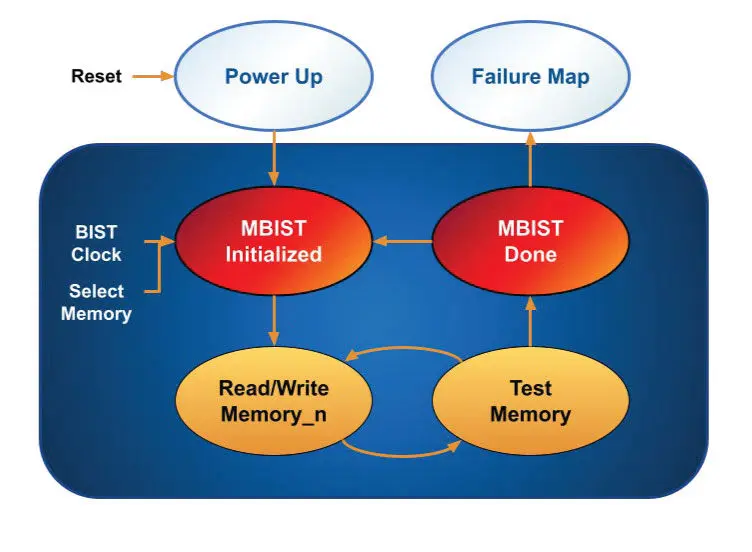

-> Programmable Test Algorithms

-> Single Error-Correcting and Double Error-Detecting

Codes on memories

-> Memory Column Repair

-> Serial error bus and remote address / data generators to

remove hundreds of wires from MBIST

-> Compatibility with third-party MemoryIP

-> User-Friendly GUI

Figure 1: MemoryRx MBIST Controller